# NCT5104D Nuvoton 4 COM IC

Date: June 28<sup>th</sup>, 2017 Revision 1.9

# Table of Contents -

| 1.  | GENERAL DESCRIPTION                              |            |

|-----|--------------------------------------------------|------------|

| 2.  | FEATURES                                         | 2          |

| 3.  | BLOCK DIAGRAM                                    | 3          |

| 4.  | PIN LAYOUT                                       | 4          |

| 5.  |                                                  | 5          |

|     |                                                  | 6          |

| _   |                                                  | 6          |

|     |                                                  | 8          |

| _   |                                                  | 8          |

| _   |                                                  | 8          |

| ٥.  | ·                                                | 8          |

|     | ,                                                | 9          |

|     | •                                                |            |

| 5.  | •                                                |            |

| 5.  | 5.7 INTERNAL PULL-UP, PULL-DOWN PINS             |            |

| 6.  | CONFIGURATION REGISTER ACCESS PROTOCOL           |            |

| 6.  | 6.1 CONFIGURATION SEQUENCE                       | 14         |

| -   |                                                  |            |

|     | 6.1.2 Configure the Configuration Registers      |            |

|     | , , , , , , , , , , , , , , , , , , , ,          |            |

|     | 6.1.4 Software Programming Example               |            |

| 7.  | UART PORT                                        |            |

| 7.  | 7.1 UART CONTROL REGISTER (UCR) (READ/WRITE)     |            |

| 7.  |                                                  |            |

|     |                                                  | TE)        |

|     |                                                  | ·)         |

| 7.  | 7.5 UART FIFO CONTROL REGISTER (UFR) (WRITE ONI  | Y)20       |

| 7.  | 7.6 INTERRUPT STATUS REGISTER (ISR) (READ ONLY)  |            |

| 7.  | 7.7 INTERRUPT CONTROL REGISTER (ICR) (READ/WRITE | )21        |

| 7.  | 7.8 PROGRAMMABLE BAUD GENERATOR (BLL/BHL) (R     | EAD/WRITE) |

| 7.  | 7.9 USER-DEFINED REGISTER (UDR) (READ/WRITE)     | 23         |

| 7.  |                                                  | 23         |

| 7.  | 7.11 UART RS485 AUTO FLOW CONTROL                | 23         |

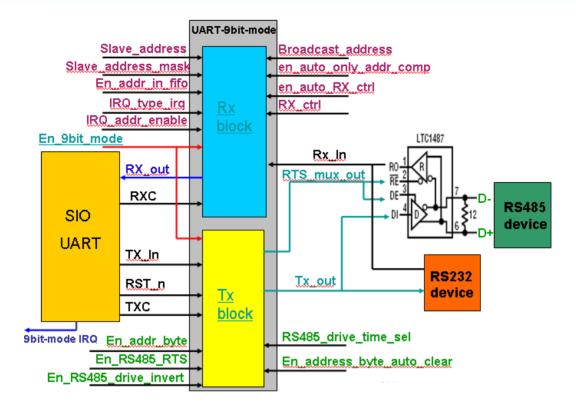

| 7.  | 7.12 UART 9BIT-MODE                              | 24         |

|     | 7.12.1 Function Dscription                       |            |

|     | 7.12.2 Function Block                            |            |

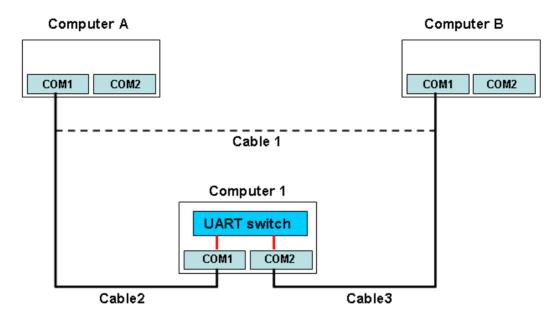

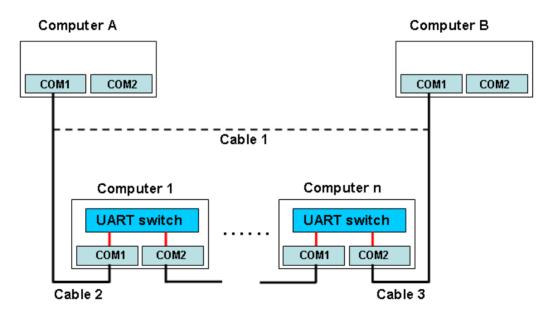

|     | 7.12.3 UART switch                               |            |

| 8.  | SERIALIZED IRQ                                   | 29         |

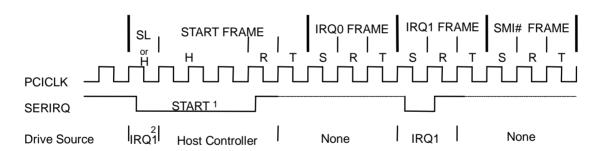

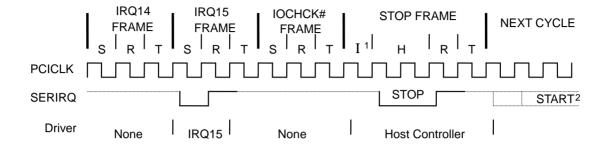

| 8.  | 8.1 START FRAME                                  | 29         |

|     |                                                  |            |

|     | •                                                | 30         |

| 9.  | WATCHDOG TIMER                                   | 32         |

| 10. | . GENERAL PURPOSE I/O                            |            |

| 10  | 10.1 GPIO ARCHITECTURE                           |            |

| 10.2 | ACCESS CHANNELS                | 35 |

|------|--------------------------------|----|

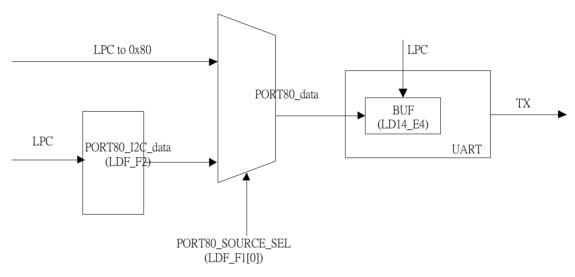

| 11.  | PORT80 TO UART                 | 36 |

| 12.  | CONFIGURATION REGISTER         | 37 |

| 12.1 | CHIP (GLOBAL) CONTROL REGISTER | 37 |

| 12.2 | LOGICAL DEVICE 2 (UARTA)       | 44 |

| 12.3 | LOGICAL DEVICE 3 (UARTB)       | 49 |

| 12.4 | LOGICAL DEVICE 7 (GPIO)        | 54 |

| 12.5 | LOGICAL DEVICE 8 (GPIO, WDT1)  | 59 |

| 12.6 | LOGICAL DEVICE 9 (GPIO)        | 63 |

| 12.7 | LOGICAL DEVICE F (GPIO)        | 64 |

| 12.8 | LOGICAL DEVICE 10 (UARTC)      | 66 |

| 12.9 | LOGICAL DEVICE 11 (UARTD)      | 71 |

| 12.1 | .0 LOGICAL DEVICE 14 (PORT80)  | 76 |

| 13.  | SPECIFICATIONS                 | 79 |

| 13.1 | ABSOLUTE MAXIMUM RATINGS       | 79 |

| 13.2 | DC CHARACTERISTICS             | 79 |

| 14.  | AC CHARACTERISTICS             | 82 |

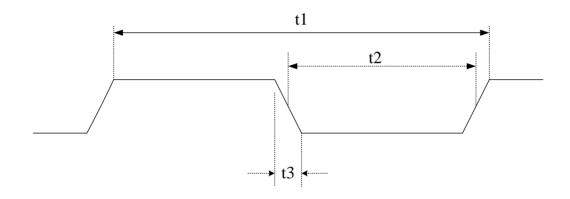

| 14.1 | CLOCK INPUT TIMING             | 82 |

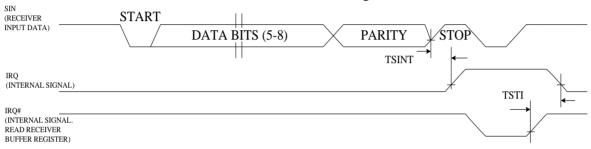

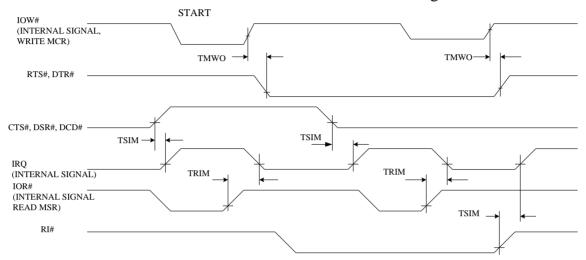

| 14.2 | UART                           | 82 |

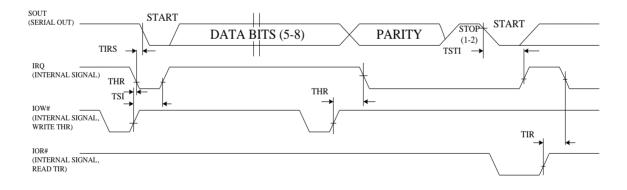

| 14.3 | MODEM CONTROL TIMING           | 84 |

| 14.4 | GPIO TIMING PARAMETERS         | 85 |

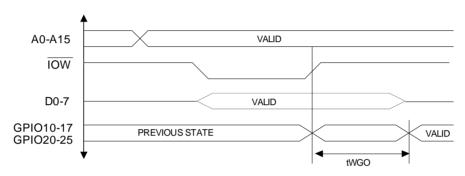

| 14   | 4.4.1 GPIO Write Timing        | 85 |

| 15.  | TOP MARKING SPECIFICATIONS     | 86 |

| 16.  | ORDERING INFORMATION           | 87 |

| 17.  | PACKAGE SPECIFICATION          | 88 |

| 18.  | REVISION HISTORY               | 89 |

# **NCT5104D**

# **LIST OF FIGURE**

| Figure 3-1 NCT5104D Block Diagram                                      | 3  |

|------------------------------------------------------------------------|----|

| Figure 4-1 NCT5104D Pin Layout                                         | 4  |

| Figure 6-1 Structure of the Configuration Register                     | 12 |

| Figure 6-2 Configuration Register                                      | 14 |

| Figure 8-1 Start Frame Timing with Source Sampled A Low Pulse on IRQ1  | 29 |

| Figure 8-2 Stop Frame Timing with Host Using 17 SERIRQ Sampling Period | 31 |

| Figure 11-1 PORT80 to UART Block Diagram                               | 36 |

|                                                                        |    |

| LIST OF TABLE                                                          |    |

| Table 6-1 Devices of I/O Base Address                                  |    |

| Table 7-1 Register Summary for UART                                    | 17 |

| Table 8-1 SERIRQ Sampling Periods                                      |    |

| Table 10-1 GPIO Group Programming Table                                | 33 |

| Table 10-2 GPIO Multi-Function Routing Table                           | 34 |

| Table 10-3 GPIO Register Addresses                                     | 35 |

|                                                                        |    |

#### 1. GENERAL DESCRIPTION

The NCT5104D is a LPC to UART IC, which supports 4 high-speed serial communication port (UART). Each UART includes a 128-byte send/receive FIFO, a programmable baud rate generator, complete modem-control capability, and a processor interrupt system. The UART supports legacy speeds up to 115.2K bps as well as even higher baud rates of 230K, 460K, or 921K bps to support higher speed modems.

In addition to UART, the NCT5104D provides flexible I/O control functions through a set of general purpose I/O (GPIO) ports. These GPIO ports may serve as simple I/O ports or may be individually configured to provide alternative functions. The NCT5104D supports port 80 decode on the LPC bus and could output the signal via SOUTC. It also supports LED control.

The configuration registers inside the NCT5104D support mode selection, function enable and disable, and power-down selection. Furthermore, the configurable PnP features are compatible with the plug-and-play feature in Windows, making the allocation of the system resources more efficient than ever.

Publication Release Date: June 28, 2017

### 2. FEATURES

#### General

Meet LPC Spec. 1.1

Support SERIRQ (Serialized IRQ)

Support DPM (Device Power Management)

Programmable configuration settings

Single 24-MHz or 48-MHz clock input

Support selective pins of 5 V tolerance

#### **UART**

Support 4 high-speed, 16550-compatible UART with 128-byte send / receive FIFO

Support RS485 auto flow control

Fully programmable serial-interface characteristics:

- --- 5, 6, 7 or 8-bit characters

- --- Even, odd or no parity bit generation / detection

- --- 1, 1.5 or 2 stop-bit generation

Internal diagnostic capabilities:

- --- Loop-back controls for communications link fault isolation

- --- Break, parity, overrun, framing error simulation

Programmable baud rate generator allows division of clock source by any value from 1 to (2<sup>16</sup>-1)

Maximum baud rate for clock source 14.769 MHz is up to 921K bps. The baud rate at 24 MHz is 1.5 M bps.

### **General Purpose I/O Ports**

GPIO0 ~ GPIO1 programmable general purpose I/O ports

Two access channels, indirect (via 2E/2F or 4E/4F) and direct (Base Address) access.

# **Watch Dog Timer Function**

#### **LED Function**

This is multi-function with some GPIO pins

### **Operation voltage**

3.3 voltage

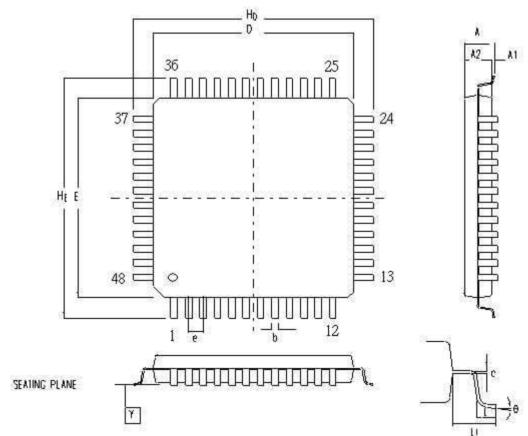

#### **Package**

48-pin LQFP

Green

Publication Release Date: June 28, 2017

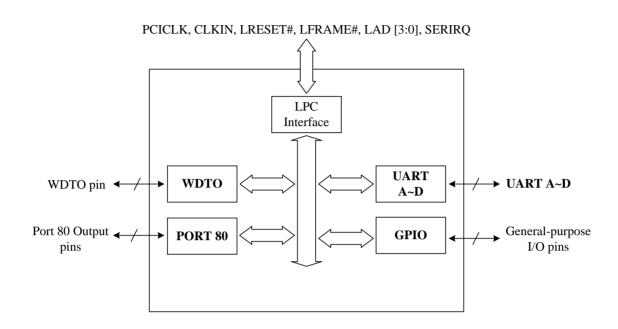

### 3. BLOCK DIAGRAM

Figure 3-1 NCT5104D Block Diagram

Publication Release Date: June 28, 2017

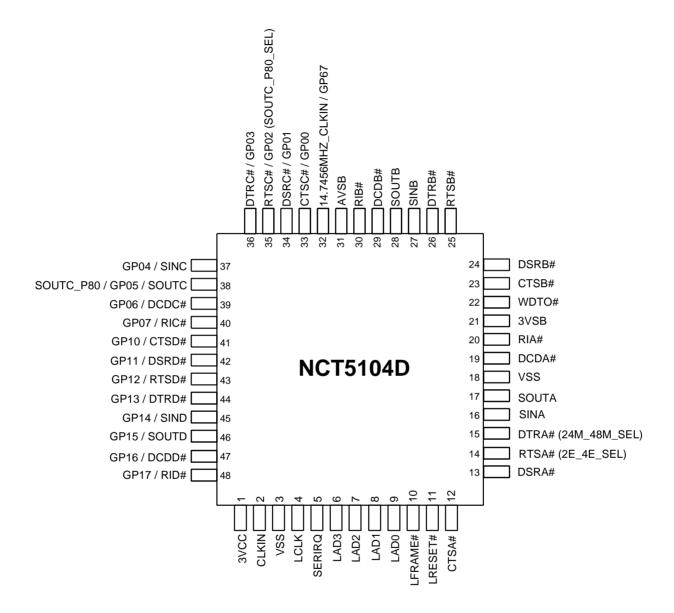

### 4. PIN LAYOUT

Figure 4-1 NCT5104D Pin Layout

Publication Release Date: June 28, 2017

### 5. PIN DESCRIPTION

Note: Please refer to 13.2 DC CHARACTERISTICS for details.

AOUT - Analog output pin

AIN - Analog input pin

$IN_{to3}$  - 3.3V TTL-level input pin

IN<sub>tso3</sub> - 3.3V TTL-level, Schmitt-trigger input pin

$IN_{gp5}$  - 5V GTL-level input pin  $IN_{tn5}$  - 5V TTL-level input pin

${\sf IN}_{\sf tscun5}$  - 5V TTL-level, Schmitt-trigger, input buffer with controllable pull-up

IN<sub>tsp5</sub> - 5V TTL-level, Schmitt-trigger input pin

$IN_{tdp5}$  - 5V TTL-level input pin with internal pull-down resistor  $IN_{tup5}$  - 5V TTL-level input pin with internal pull-up resistor

O<sub>8</sub> - output pin with 8-mA source-sink capability OD<sub>8</sub> - open-drain output pin with 8-mA sink capability O<sub>12</sub> - output pin with 12-mA source-sink capability  $OD_{12}$ - open-drain output pin with 12-mA sink capability  $O_{24}$ - output pin with 24-mA source-sink capability  $OD_{24}$ - open-drain output pin with 24-mA sink capability  $O_{48}$ - output pin with 48-mA source-sink capability  $OD_{48}$ - open-drain output pin with 48-mA sink capability

$I/O_{v3}$  - Bi-direction pin with source capability of 6 mA and sink capability of 1 mA

I/O<sub>v4</sub> - Bi-direction pin with source capability of 6 mA

$O_{12cu} \qquad \quad \text{- output pin 12-mA source-sink capability with controllable pull-up} \\ OD_{12cu} \qquad \quad \text{- open-drain 12-mA sink capability output pin with controllable pull-up} \\$

Publication Release Date: June 28, 2017

# 5.1 LPC Interface

| PIN | SYMBOL   | I/O | BUFFER<br>TYPE                                              | POWER<br>WELL | DESCRIPTION                                                                                                             |

|-----|----------|-----|-------------------------------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------|

| 2   | CLKIN    | I   | IN <sub>tp5</sub>                                           | VCC           | System clock input, either 24MHz or 48MHz. The actual frequency must be specified by 24M_48M_SEL strapping.             |

| 4   | LCLK     | I   | $IN_{tp3}$                                                  | VCC           | Low Pin Count interface clock, 19.2MHZ~33MHz.                                                                           |

| 5   | SERIRQ   | I/O | $\begin{matrix} IN_{tp3} \\ O_{12} \\ OD_{12} \end{matrix}$ | VCC           | Serialized IRQ input / output.                                                                                          |

| 6-9 | LAD[3:0] | I/O | IN <sub>tp3</sub><br>OD <sub>12</sub>                       | VCC           | These signal lines communicate address, control, and data information over the LPC bus between a host and a peripheral. |

| 10  | LFRAME#  | I   | IN <sub>tp3</sub>                                           | VCC           | Indicates the start of a new cycle or the termination of a broken cycle.                                                |

| 11  | LRESET#  | I   | IN <sub>tp3</sub>                                           | VCC           | Reset signal. It can be connected to the PCIRST# signal on the host.                                                    |

# 5.2 Serial Port Interface

| PIN | SYMBOL | I/O | BUFFER<br>TYPE    | POWER<br>WELL | DESCRIPTION                                                                                                                                    |

|-----|--------|-----|-------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 20  | RIA#   | I   | IN <sub>tp5</sub> | VSB           | Ring Indicator. An active-low signal indicates that a ring signal is being received from the modem or the data set.                            |

| 19  | DCDA#  | _   | IN <sub>tp5</sub> | VSB           | Data Carrier Detection. An active-low signal indicates the modem or data set has detected a data carrier.                                      |

| 17  | SOUTA  | 0   | O <sub>12</sub>   | VSB           | UART A Serial Output. This pin is used to transmit serial data out to the communication link.                                                  |

| 16  | SINA   | -   | IN <sub>tp5</sub> | VSB           | Serial Input. This pin is used to receive serial data through the communication link.                                                          |

| 15  | DTRA#  | 0   | O <sub>12</sub>   | VSB           | UART A Data Terminal Ready. An active-low signal informs the modem or data set that the controller is ready to communicate.                    |

| 14  | RTSA#  | 0   | O <sub>12</sub>   | VSB           | UART A Request To Send. An active-low signal informs the modem or data set that the controller is ready to send data.                          |

| 13  | DSRA#  | I   | IN <sub>tp5</sub> | VSB           | Data Set Ready. An active-low signal indicates the modem or data set is ready to establish a communication link and transfer data to the UART. |

| 12  | CTSA#  | I   | IN <sub>tp5</sub> | VSB           | Clear To Send. This is the modem-control input. The function of these pins can be tested by reading bit 4 of the handshake status register.    |

| 30  | RIB#   | I   | IN <sub>tp5</sub> | VSB           | Ring Indicator. An active-low signal indicates that a ring signal is being received from the modem or the data set.                            |

| 29  | DCDB#  | I   | IN <sub>tp5</sub> | VSB           | Data Carrier Detection. An active-low signal indicates the modem or data set has detected a data carrier.                                      |

Publication Release Date: June 28, 2017

| PIN | SYMBOL    | I/O | BUFFER<br>TYPE    | POWER<br>WELL | DESCRIPTION                                                                                                                                    |

|-----|-----------|-----|-------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 28  | SOUTB     | 0   | O <sub>12</sub>   | VSB           | UART B Serial Output. This pin is used to transmit serial data out to the communication link.                                                  |

| 27  | SINB      | I   | IN <sub>tp5</sub> | VSB           | Serial Input. This pin is used to receive serial data through the communication link.                                                          |

| 26  | DTRB#     | 0   | O <sub>12</sub>   | VSB           | UART B Data Terminal Ready. An active-low signal informs the modem or data set that the controller is ready to communicate.                    |

| 25  | RTSB#     | 0   | O <sub>12</sub>   | VSB           | UART B Request To Send. An active-low signal informs the modem or data set that the controller is ready to send data.                          |

| 24  | DSRB#     | -   | IN <sub>tp5</sub> | VSB           | Data Set Ready. An active-low signal indicates the modem or data set is ready to establish a communication link and transfer data to the UART. |

| 23  | CTSB#     | -   | IN <sub>tp5</sub> | VSB           | Clear To Send. This is the modem-control input. The function of these pins can be tested by reading bit 4 of the handshake status register.    |

| 40  | RIC#      |     | IN <sub>tp5</sub> | VSB           | Ring Indicator. An active-low signal indicates that a ring signal is being received from the modem or the data set.                            |

| 39  | DCDC#     |     | IN <sub>tp5</sub> | VSB           | Data Carrier Detection. An active-low signal indicates the modem or data set has detected a data carrier.                                      |

| 38  | SOUTC     | 0   | O <sub>12</sub>   | VSB           | UART C Serial Output. This pin is used to transmit serial data out to the communication link.                                                  |

| 38  | SOUTC_P80 | 0   | O <sub>12</sub>   | VSB           | PORT80 to UART Serial Output. This pin is used to transmit serial data out to the communication link.                                          |

| 37  | SINC      | l   | IN <sub>tp5</sub> | VSB           | Serial Input. This pin is used to receive serial data through the communication link.                                                          |

| 36  | DTRC#     | 0   | O <sub>12</sub>   | VSB           | UART C Data Terminal Ready. An active-low signal informs the modem or data set that the controller is ready to communicate.                    |

| 35  | RTSC#     | 0   | O <sub>12</sub>   | VSB           | UART C Request To Send. An active-low signal informs the modem or data set that the controller is ready to send data.                          |

| 34  | DSRC#     | ı   | IN <sub>tp5</sub> | VSB           | Data Set Ready. An active-low signal indicates the modem or data set is ready to establish a communication link and transfer data to the UART. |

| 33  | CTSC#     | ı   | IN <sub>tp5</sub> | VSB           | Clear To Send. This is the modem-control input. The function of these pins can be tested by reading bit 4 of the handshake status register.    |

| 48  | RID#      | I   | IN <sub>tp5</sub> | VSB           | Ring Indicator. An active-low signal indicates that a ring signal is being received from the modem or the data set.                            |

| 47  | DCDD#     | I   | IN <sub>tp5</sub> | VSB           | Data Carrier Detection. An active-low signal indicates the modem or data set has detected a data carrier.                                      |

| 46  | SOUTD     | 0   | O <sub>12</sub>   | VSB           | UART D Serial Output. This pin is used to transmit serial data out to the communication link.                                                  |

| PIN | SYMBOL               | I/O | BUFFER<br>TYPE    | POWER<br>WELL | DESCRIPTION                                                                                                                                    |

|-----|----------------------|-----|-------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 45  | SIND                 | l   | IN <sub>tp5</sub> | VSB           | Serial Input. This pin is used to receive serial data through the communication link.                                                          |

| 44  | DTRD#                | 0   | O <sub>12</sub>   | VSB           | UART D Data Terminal Ready. An active-low signal informs the modem or data set that the controller is ready to communicate.                    |

| 43  | RTSD#                | 0   | O <sub>12</sub>   | VSB           | UART D Request To Send. An active-low signal informs the modem or data set that the controller is ready to send data.                          |

| 42  | DSRD#                | ı   | IN <sub>tp5</sub> | VSB           | Data Set Ready. An active-low signal indicates the modem or data set is ready to establish a communication link and transfer data to the UART. |

| 41  | CTSD#                | I   | IN <sub>tp5</sub> | VSB           | Clear To Send. This is the modem-control input. The function of these pins can be tested by reading bit 4 of the handshake status register.    |

| 32  | 14.7456MHZ<br>_CLKIN | I   | IN <sub>tp5</sub> | VSB           | UART-clock 14.7456-MHz input                                                                                                                   |

### 5.3 Power Pins

| PIN   | SYMBOL | I/O | BUFFER<br>TYPE | POWER<br>WELL | DESCRIPTION                                                                |

|-------|--------|-----|----------------|---------------|----------------------------------------------------------------------------|

| 21    | 3VSB   | I   |                | 3VSB          | +3.3 V stand-by power supply for the digital circuits.                     |

| 1     | 3VCC   | I   |                | 3VCC          | +3.3 V power supply for driving 3 V on host interface.                     |

| 31    | AVSB   | I   |                | AVSB          | Analog +3.3 V power input. Internally supply power to all analog circuits. |

| 3, 18 | VSS    | I   |                | VSS           | Ground.                                                                    |

# 5.4 WatchDog

| PIN | SYMBOL | I/O | BUFFER<br>TYPE | POWER<br>WELL | DESCRIPTION                   |

|-----|--------|-----|----------------|---------------|-------------------------------|

| 22  | WDTO#  | 0   |                | VSB           | Watchdog Timer output signal. |

# 5.5 General Purpose I/O Port

# 5.5.1 GPIO-0 Interface

| PIN | SYMBOL | I/O | BUFFER<br>TYPE                                           | POWER<br>WELL | DESCRIPTION                       |

|-----|--------|-----|----------------------------------------------------------|---------------|-----------------------------------|

| 33  | GP00   | I/O | IN <sub>tp5</sub><br>O <sub>12</sub><br>OD <sub>12</sub> | VSB           | General-purpose I/O port 0 bit 0. |

| PIN | SYMBOL | I/O | BUFFER<br>TYPE                                                                                                     | POWER<br>WELL | DESCRIPTION                       |

|-----|--------|-----|--------------------------------------------------------------------------------------------------------------------|---------------|-----------------------------------|

| 34  | GP01   | I/O | $\begin{array}{c} \text{IN}_{\text{tp5}} \\ \text{O}_{\text{12}} \\ \text{OD}_{\text{12}} \end{array}$             | VSB           | General-purpose I/O port 0 bit 1. |

| 35  | GP02   | I/O | $\begin{array}{c} \mathrm{IN}_{\mathrm{tp5}} \\ \mathrm{O}_{\mathrm{12}} \\ \mathrm{OD}_{\mathrm{12}} \end{array}$ | VSB           | General-purpose I/O port 0 bit 2. |

| 36  | GP03   | I/O | IN <sub>tp5</sub> O <sub>12</sub> OD <sub>12</sub>                                                                 | VSB           | General-purpose I/O port 0 bit 3. |

| 37  | GP04   | I/O | IN <sub>tp5</sub> O <sub>12</sub> OD <sub>12</sub>                                                                 | VSB           | General-purpose I/O port 0 bit 4. |

| 38  | GP05   | I/O | $\begin{array}{c} \text{IN}_{\text{tp5}} \\ \text{O}_{\text{12}} \\ \text{OD}_{\text{12}} \end{array}$             | VSB           | General-purpose I/O port 0 bit 5. |

| 39  | GP06   | I/O | IN <sub>tp5</sub><br>O <sub>12</sub><br>OD <sub>12</sub>                                                           | VSB           | General-purpose I/O port 0 bit 6. |

| 40  | GP07   | I/O | $\begin{array}{c} \text{IN}_{\text{tp5}} \\ \text{O}_{\text{12}} \\ \text{OD}_{\text{12}} \end{array}$             | VSB           | General-purpose I/O port 0 bit 7. |

# 5.5.2 GPIO-1 Interface

| PIN | SYMBOL | I/O | BUFFER<br>TYPE                                                                                                     | POWER<br>WELL | DESCRIPTION                       |

|-----|--------|-----|--------------------------------------------------------------------------------------------------------------------|---------------|-----------------------------------|

| 41  | GP10   | I/O | IN <sub>tp5</sub><br>O <sub>12</sub><br>OD <sub>12</sub>                                                           | VSB           | General-purpose I/O port 1 bit 0. |

| 42  | GP11   | I/O | $\begin{array}{c} \text{IN}_{\text{tp5}} \\ \text{O}_{\text{12}} \\ \text{OD}_{\text{12}} \end{array}$             | VSB           | General-purpose I/O port 1 bit 1. |

| 43  | GP12   | I/O | $\begin{array}{c} \mathrm{IN}_{\mathrm{tp5}} \\ \mathrm{O}_{\mathrm{12}} \\ \mathrm{OD}_{\mathrm{12}} \end{array}$ | VSB           | General-purpose I/O port 1 bit 2. |

| 44  | GP13   | I/O | IN <sub>tp5</sub><br>O <sub>12</sub><br>OD <sub>12</sub>                                                           | VSB           | General-purpose I/O port 1 bit 3. |

| PIN | SYMBOL | I/O | BUFFER<br>TYPE                                                                                                     | POWER<br>WELL | DESCRIPTION                       |

|-----|--------|-----|--------------------------------------------------------------------------------------------------------------------|---------------|-----------------------------------|

| 45  | GP14   | I/O | $\begin{array}{c} \text{IN}_{\text{tp5}} \\ \text{O}_{\text{12}} \\ \text{OD}_{\text{12}} \end{array}$             | VSB           | General-purpose I/O port 1 bit 4. |

| 46  | GP15   | I/O | $\begin{array}{c} \text{IN}_{\text{tp5}} \\ \text{O}_{\text{12}} \\ \text{OD}_{\text{12}} \end{array}$             | VSB           | General-purpose I/O port 1 bit 5. |

| 47  | GP16   | I/O | $\begin{array}{c} \text{IN}_{\text{tp5}} \\ \text{O}_{\text{12}} \\ \text{OD}_{\text{12}} \end{array}$             | VSB           | General-purpose I/O port 1 bit 6. |

| 48  | GP17   | I/O | $\begin{array}{c} \mathrm{IN}_{\mathrm{tp5}} \\ \mathrm{O}_{\mathrm{12}} \\ \mathrm{OD}_{\mathrm{12}} \end{array}$ | VSB           | General-purpose I/O port 1 bit 7. |

# 5.5.3 GPIO-6 Interface

| PIN | SYMBOL | I/O | BUFFER<br>TYPE                                               | POWER<br>WELL | DESCRIPTION                       |

|-----|--------|-----|--------------------------------------------------------------|---------------|-----------------------------------|

| 32  | GP67   | I/O | $\begin{array}{c} IN_{tp5} \\ O_{12} \\ OD_{12} \end{array}$ | VSB           | General-purpose I/O port 6 bit 7. |

# 5.6 Strapping Pins

| PIN | SYMBOL          | I/O | BUFFER<br>TYPE     | POWER<br>WELL | DESCRIPTION                                                                                                                                                                                         |

|-----|-----------------|-----|--------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14  | 2E_4E_SEL       | I   | IN <sub>tdp5</sub> | VSB           | NCT5104D I/O address selection. (Strapped by LRESET#)  Strapped to high: NCT5104D I/O address is 4Eh/4Fh. Strapped to low: NCT5104D I/O address is 2Eh/2Fh.                                         |

| 15  | 24M_48M_S<br>EL | I   | IN <sub>tdp5</sub> | VSB           | Input clock rate selection (Strapped by VCC [internal Power OK signal without any delay])  Strapped to high: The clock input on pin 2 is 48MHz. Strapped to low: The clock input on pin 2 is 24MHz. |

-10-

Publication Release Date: June 28, 2017

| PIN | SYMBOL            | I/O | BUFFER<br>TYPE     | POWER<br>WELL | DESCRIPTION                                                                                                           |

|-----|-------------------|-----|--------------------|---------------|-----------------------------------------------------------------------------------------------------------------------|

| 35  | SOUTC_P80_<br>SEL | I   | IN <sub>tdp5</sub> | VSB           | Pin38 function selection. (Strapped by VCC [internal Power OK signal without any delay])  See configuration register. |

Note. All Strapping results can be programming by LPC Interface. There are three conditions below:

- 1) VSB Strapping result can be programming by LPC, and reset by RSMRST#.

- 2) VCC Strapping result can be programming by LPC, and reset by PWROK.

- 3) LRESET# Strapping (2E\_4E\_SEL) can be programming by LPC, and reset by LRESET#.

# 5.7 Internal pull-up, pull-down pins

| Signal         | Pin(s) | Power<br>well | Туре          | Resistor | Note |  |  |  |  |  |

|----------------|--------|---------------|---------------|----------|------|--|--|--|--|--|

| Strapping Pins |        |               |               |          |      |  |  |  |  |  |

| 2E_4E_SEL      | 14     | VSB           | Pull-<br>down | 47.4K    | 1    |  |  |  |  |  |

| 24M_48M_SEL    | 15     | VSB           | Pull-<br>down | 47.4K    | 1    |  |  |  |  |  |

| SOUTC_P80_SEL  | 35     | VSB           | Pull-<br>down | 47.4K    | 1    |  |  |  |  |  |

Note1. Active only during VCC Power-up reset

Publication Release Date: June 28, 2017

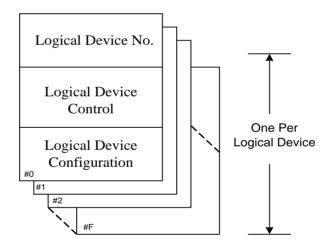

#### 6. CONFIGURATION REGISTER ACCESS PROTOCOL

The NCT5104D uses a special protocol to access configuration registers to set up different types of configurations. The NCT5104D has the following Logical Devices: UARTA (Logical Device 2), UARTB (Logical Device 3), GPIO (Logical Device 7), GPIO & WDT1 (Logical Device 8), GPIO (Logical Device F), UARTC (Logical Device 10), UARTD (Logical Device 11), and PORT80 (Logical Device 14).

It would require a large address space to access all of the logical device configuration registers if they were mapped into the normal PC address space. The NCT5104D, then, maps all the configuration registers through two I/O addresses (2Eh/2Fh or 4Eh/4Fh) set at power on by the strap pin 2E\_4E\_SEL. The two I/O addresses act as an index/data pair to read or write data to the NCT5104D. One must write an index to the first I/O address which points to the register and read or write to the second address which acts as a data register.

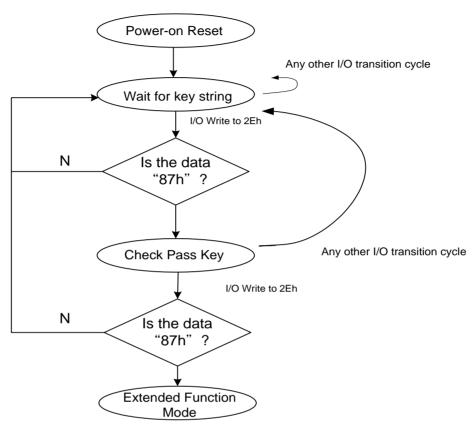

An extra level of security is added by only allowing data updates when the NCT5104D is in a special mode, called the Extended Function Mode. This mode is entered by two successive writes of 87h data to the first I/O address. This special mode ensures no false data can corrupt the NCT5104D configuration during a program runaway.

There are a set of global registers located at index 0h - 2Fh, containing information and configuration for the entire chip.

The method to access the control registers of the individual logical devices is straightforward. Simply write the desired logical device number into the global register 07h. Subsequent accesses with indexes of 30h or higher are directly to the logical device registers.

Figure 6-1 Structure of the Configuration Register

Publication Release Date: June 28, 2017

Table 6-1 Devices of I/O Base Address

| LOGICAL DEVICE<br>NUMBER | FUNCTION   | I/O BASE ADDRESS |

|--------------------------|------------|------------------|

| 0                        | Reserve    | ed               |

| 1                        | Reserve    | ed               |

| 2                        | UARTA      | 100h ~ FF8h      |

| 3                        | UARTB      | 100h ~ FF8h      |

| 4                        | Reserve    | ed               |

| 5                        | Reserve    | ed               |

| 6                        | Reserve    | ed               |

| 7                        | GPIO       | Reserved         |

| 8                        | GPIO, WDT1 | Reserved         |

| 9                        | Reserve    | ed               |

| A                        | Reserve    | ed               |

| В                        | Reserve    | ed               |

| С                        | Reserve    | ed               |

| D                        | Reserve    | ed               |

| E                        | Reserve    | ed               |

| F                        | GPIO       | Reserved         |

| 10                       | UARTC      | 100h ~ FF8h      |

| 11                       | UARTD      | 100h ~ FF8h      |

| 12                       | Reserve    | ed               |

| 13                       | Reserve    | ed               |

| 14                       | PORT80     | 100h ~ FF8h      |

| 15                       | Reserve    | ed               |

| 16                       | Reserve    | ed               |

### 6.1 Configuration Sequence

Figure 6-2 Configuration Register

To program the NCT5104D configuration registers, the following configuration procedures must be followed in sequence:

- (1). Enter the Extended Function Mode.

- (2). Configure the configuration registers.

- (3). Exit the Extended Function Mode.

#### 6.1.1 Enter the Extended Function Mode

To place the chip into the Extended Function Mode, two successive writes of 0x87 must be applied to Extended Function Enable Registers (EFERs, i.e. 2Eh or 4Eh).

### 6.1.2 Configure the Configuration Registers

The chip selects the Logical Device and activates the desired Logical Devices through Extended Function Index Register (EFIR) and Extended Function Data Register (EFDR). The EFIR is located at the same address as the EFER, and the EFDR is located at address (EFIR+1).

First, write the Logical Device Number (i.e. 0x07) to the EFIR and then write the number of the desired Logical Device to the EFDR. If accessing the Chip (Global) Control Registers, this step is not required.

Second, write the address of the desired configuration register within the Logical Device to the EFIR and then write (or read) the desired configuration register through the EFDR.

Publication Release Date: June 28, 2017

#### 6.1.3 Exit the Extended Function Mode

To exit the Extended Function Mode, writing 0xAA to the EFER is required. Once the chip exits the Extended Function Mode, it is in the normal running mode and is ready to enter the configuration mode.

#### 6.1.4 Software Programming Example

The following example is written in Intel 8086 assembly language. It assumes that the EFER is located at 2Eh, so the EFIR is located at 2Eh and the EFDR is located at 2Fh. If the HEFRAS (CR [26h] bit 6 showing the value of the strap pin at power on) is set, 2Eh can be directly replaced by 4Eh and 2Fh replaced by 4Fh.

This example programs the configuration register F0h (clock source) of logical device 1 (UART A) to the value of 3Ch (24MHz). First, one must enter the Extended Function Mode, then setting the Logical Device Number (Index 07h) to 01h. Then program index F0h to 3Ch. Finally, exit the Extended Function Mode.

```

·-----

; Enter the Extended Function Mode

•_____

MOV

DX, 2EH

MOV

AL, 87H

OUT

DX, AL

OUT

DX, AL

; Configure Logical Device 1, Configuration Register CRF0

MOV

DX, 2EH

MOV

AL, 07H

OUT

DX, AL

; point to Logical Device Number Reg.

MOV

DX, 2FH

MOV

AL, 01H

OUT

DX. AL

; select Logical Device 1

MOV

DX. 2EH

MOV

AL, F0H

DX, AL

OUT

: select CRF0

MOV

DX, 2FH

AL, 3CH

MOV

OUT

DX. AL

; update CRF0 with value 3CH

._____

: Exit the Extended Function Mode

·-----

MOV

DX, 2EH

MOV

AL, AAH

OUT

DX, AL

```

Publication Release Date: June 28, 2017

### 7. UART PORT

NCT5104D supports 4 UART – UART A, UART B, UART C, and UART D.

# 7.1 UART Control Register (UCR) (Read/Write)

The UART Control Register defines and controls the protocol for asynchronous data communications; including data length, stop bit, parity, and baud rate selection.

| BIT     | 7     | 6   | 5    | 4   | 3   | 2    | 1    | 0    |

|---------|-------|-----|------|-----|-----|------|------|------|

| NAME    | BDLAB | SSE | PBFE | EPE | PBE | MSBE | DLS1 | DLS0 |

| DEFAULT | 0     | 0   | 0    | 0   | 0   | 0    | 0    | 0    |

| BIT | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | BDLAB (Baud Rate Divisor Latch Access Bit). When this bit is set to logic 1, designers can access the divisor (in 16-bit binary format) from the divisor latches of the baud-rate generator during a read or write operation. When this bit is set to logic 0, the Receiver Buffer Register, the Transmitter Buffer Register, and the Interrupt Control Register can be accessed.                                                                                |

| 6   | <b>SSE (Set Silence Enable).</b> A logic 1 forces the Serial Output (SOUT) to a silent state (a logical 0). Only IRTX is affected by this bit; the transmitter is not affected.                                                                                                                                                                                                                                                                                  |

| 5   | PBFE (Parity Bit Fixed Enable). When PBE and PBFE of UCR are both set to logic 1, (1) if EPE is logic 1, the parity bit is logical 0 when transmitting and checking; (2) if EPE is logic 0, the parity bit is logical 1 when transmitting and checking.                                                                                                                                                                                                          |

| 4   | <b>EPE (Even Parity Enable).</b> When PBE is set to logic 1, this bit counts the number of logic 1's in the data word bits and determines the parity bit. When this bit is set to logic 1, the parity bit is set to logic 1 if an even number of logic 1's are sent or checked. When the bit is set to logic 0, the parity bit is logic 1, if an odd number of logic 1's are sent or checked.                                                                    |

| 3   | <b>PBE (Parity Bit Enable).</b> When this bit is set to logic 1, the transmitter inserts a stop bit between the last data bit and the stop bit of the SOUT, and the receiver checks the parity bit in the same position.                                                                                                                                                                                                                                         |

| 2   | <ul> <li>MSBE (Multiple Stop Bit Enable). Defines the number of stop bits in each serial character that is transmitted or received.</li> <li>(1) If MSBE is set to logic 0, one stop bit is sent and checked.</li> <li>(2) If MSBE is set to logic 1 and the data length is 5 bits, one-and-a-half stop bits are sent and checked.</li> <li>(3) If MSBE is set to logic 1 and the data length is 6, 7, or 8 bits, two stop bits are sent and checked.</li> </ul> |

| 1   | <b>DLS1 (Data Length Select Bit 1).</b> Defines the number of data bits that are sent or checked in each serial character.                                                                                                                                                                                                                                                                                                                                       |

| 0   | <b>DLS0 (Data Length Select Bit 0).</b> Defines the number of data bits that are sent or checked in each serial character.                                                                                                                                                                                                                                                                                                                                       |

| DLS1 | DLS0 | DATA LENGTH |

|------|------|-------------|

| 0    | 0    | 5 bits      |

| 0    | 1    | 6 bits      |

| 1    | 0    | 7 bits      |

| DLS1 | DLS0 | DATA LENGTH |

|------|------|-------------|

| 1    | 1    | 8 bits      |

The following table identifies the remaining UART registers. Each one is described separately in the following sections.

Table 7-1 Register Summary for UART

|                  |                                                  |     |                                                     |                                                 | Bit N                                     | umber                                 |                                     |                                        |                                          |                                             |

|------------------|--------------------------------------------------|-----|-----------------------------------------------------|-------------------------------------------------|-------------------------------------------|---------------------------------------|-------------------------------------|----------------------------------------|------------------------------------------|---------------------------------------------|

| Register         | Address Base                                     |     | 0                                                   | 1                                               | 2                                         | 3                                     | 4                                   | 5                                      | 6                                        | 7                                           |

| + 0<br>BDLAB = 0 | Receiver<br>Buffer<br>Register<br>(Read Only)    | RBR | RX Data<br>Bit 0                                    | RX Data<br>Bit 1                                | RX Data<br>Bit 2                          | RX Data<br>Bit 3                      | RX Data<br>Bit 4                    | RX Data<br>Bit 5                       | RX Data<br>Bit 6                         | RX Data<br>Bit 7                            |

| + 0<br>BDLAB = 0 | Transmitter<br>Buffer Register<br>(Write Only)   | TBR | TX Data<br>Bit 0                                    | TX Data<br>Bit 1                                | TX Data<br>Bit 2                          | TX Data<br>Bit 3                      | TX Data<br>Bit 4                    | TX Data<br>Bit 5                       | TX Data<br>Bit 6                         | TX Data<br>Bit 7                            |

| + 1<br>BDLAB = 0 | Interrupt Control<br>Register                    | ICR | RBR Data<br>Ready<br>Interrupt<br>Enable<br>(ERDRI) | TBR<br>Empty<br>Interrupt<br>Enable<br>(ETBREI) | USR<br>Interrupt<br>Enable<br>(EUSRI)     | HSR<br>Interrupt<br>Enable<br>(EHSRI) | 0                                   | 0                                      | 0                                        | 0                                           |

| +2               | Interrupt Status<br>Register<br>(Read Only)      | ISR | "0" if<br>Interrupt<br>Pending                      | Interrupt<br>Status<br>Bit (0)                  | Interrupt<br>Status<br>Bit (1)            | Interrupt<br>Status<br>Bit (2)**      | 0                                   | 0                                      | FIFOs<br>Enabled<br>**                   | FIFOs<br>Enabled<br>**                      |

| + 2              | UART FIFO<br>Control<br>Register<br>(Write Only) | UFR | FIFO<br>Enable                                      | RCVR<br>FIFO<br>Reset                           | XMIT<br>FIFO<br>Reset                     | DMA<br>Mode<br>Select                 | Reserved                            | Reversed                               | RX<br>Interrupt<br>Active Level<br>(LSB) | RX<br>Interrupt<br>Active Level<br>(MSB)    |

| +3               | UART Control<br>Register                         | UCR | Data<br>Length<br>Select<br>Bit 0<br>(DLS0)         | Data<br>Length<br>Select<br>Bit 1<br>(DLS1)     | Multiple<br>Stop Bits<br>Enable<br>(MSBE) | Parity<br>Bit<br>Enable<br>(PBE)      | Even<br>Parity<br>Enable<br>(EPE)   | Parity<br>Bit Fixed<br>Enable<br>PBFE) | Set<br>Silence<br>Enable<br>(SSE)        | Baudrate Divisor Latch Access Bit (BDLAB)   |

| + 4              | Handshake<br>Control<br>Register                 | HCR | Data<br>Terminal<br>Ready<br>(DTR)                  | Request<br>to<br>Send<br>(RTS)                  | Loopback<br>RI<br>Input                   | IRQ<br>Enable                         | Internal<br>Loopback<br>Enable      | 0                                      | 0                                        | 0                                           |

| + 5              | UART Status<br>Register                          | USR | RBR Data<br>Ready<br>(RDR)                          | Overrun<br>Error<br>(OER)                       | Parity Bit<br>Error<br>(PBER)             | No Stop<br>Bit<br>Error<br>(NSER)     | Silent<br>Byte<br>Detected<br>(SBD) | TBR<br>Empty<br>(TBRE)                 | TSR<br>Empty<br>(TSRE)                   | RX FIFO<br>Error<br>Indication<br>(RFEI) ** |

| + 6              | Handshake<br>Status Register                     | HSR | CTS<br>Toggling<br>(TCTS)                           | DSR<br>Toggling<br>(TDSR)                       | RI Falling<br>Edge<br>(FERI)              | DCD<br>Toggling<br>(TDCD)             | Clear<br>to Send<br>(CTS)           | Data Set<br>Ready<br>(DSR)             | Ring<br>Indicator<br>(RI)                | Data Carrier<br>Detect<br>(DCD)             |

| + 7              | User Defined<br>Register                         | UDR | Bit 0                                               | Bit 1                                           | Bit 2                                     | Bit 3                                 | Bit 4                               | Bit 5                                  | Bit 6                                    | Bit 7                                       |

| + 0<br>BDLAB = 1 | Baudrate<br>Divisor Latch<br>Low                 | BLL | Bit 0                                               | Bit 1                                           | Bit 2                                     | Bit 3                                 | Bit 4                               | Bit 5                                  | Bit 6                                    | Bit 7                                       |

| + 1<br>BDLAB = 1 | Baudrate<br>Divisor Latch<br>High                | BHL | Bit 8                                               | Bit 9                                           | Bit 10                                    | Bit 11                                | Bit 12                              | Bit 13                                 | Bit 14                                   | Bit 15                                      |

<sup>\*:</sup> Bit 0 is the least significant bit. The least significant bit is the first bit serially transmitted or received.

\*\*: These bits are always 0 in 16450 Mode.

# 7.2 UART Status Register (USR) (Read/Write)

This 8-bit register provides information about the status of data transfer during communication.

| BIT     | 7     | 6    | 5    | 4   | 3    | 2    | 1   | 0   |

|---------|-------|------|------|-----|------|------|-----|-----|

| NAME    | RF EI | TSRE | TBRE | SBD | NSER | PBER | OER | RDR |

| DEFAULT | 0     | 1    | 1    | 0   | 0    | 0    | 0   | 0   |

| BIT | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | RF EI (RX FIFO Error Indication). In 16450 mode, this bit is always set to logical 0. in 16550 mode, this bit is set to logical 1 when there is at least one parity-bit error and no stop0bit error or silent-byte detected in the FIFO. In 16550 mode, this bit is cleared to logical 0 by reading from the USR if there are no remaining errors left in the FIFO.                              |

| 6   | <b>TSRE (Transmitter Shift Register Empty).</b> In 16450 mode, this bit is set to logical 1 when TBR and TSR are both empty. In 16550 mode, it is set to logical 1 when the transmit FIFO and TSR are both empty. Otherwise, this bit is set to logical 0.                                                                                                                                       |

| 5   | <b>TBRE (Transmitter Buffer Register Empty).</b> In 16450 mode, when a data character is transferred from TBR to TSR, this bit is set to logical 1. If ETREI of ICR is high, and interrupt is generated to notify the CPU to write next data. In 16550 mode, this bit is set to logical 1 when the transmit FIFO is empty. It is set to logical 0 when the CPU writes data into TBR or the FIFO. |

| 4   | <b>SBD (Silent Byte Detected).</b> This bit is set to logical 1 to indicate that received data are kept in silent state for the time it takes to receive a full word, which includes the start bit, data bits, parity bit, and stop bits. In 16550 mode, it indicates the same condition for the data on the top of the FIFO. When the CPU reads USR, it sets this bit to logical 0.             |

| 3   | <b>NSER (No Stop Bit Error).</b> This bit is set to logical 1 to indicate that the received data have no stop bit. In 16550 mode, it indicates the same condition for the data on the top of the FIFO. When the CPU reads USR, it sets this bit to logical 0.                                                                                                                                    |

| 2   | <b>PBER (Parity Bit Error).</b> This bit is set to logical 1 to indicate that the received data has the wrong parity bit. In 16550 mode, it indicates the same condition for the data on the top of the FIFO. When the CPU reads USR, it sets this bit to logical 0.                                                                                                                             |

| 1   | <b>OER (Overrun Error).</b> This bit is set to logical 1 to indicate that the received data have been overwritten by the next received data before they were read by the CPU. In 16550 mode, it indicates the same condition, instead of FIFO full. When the CPU reads USR, it sets this bit to logical 0.                                                                                       |

| 0   | RDR (RBR Data Ready). This bit is set to logical 1 to indicate that the received data are ready to be read by the CPU in the RBR or FIFO. When no data are left in the RBR or FIFO, the bit is set to logical 0.                                                                                                                                                                                 |

# 7.3 Handshake Control Register (HCR) (Read/Write)

This register controls pins used with handshaking peripherals such as modems and also controls the diagnostic mode of the UART.

| BIT     | 7 6 5    |  | 4 | 3                              | 2             | 1                    | 0   |     |

|---------|----------|--|---|--------------------------------|---------------|----------------------|-----|-----|

| NAME    | RESERVED |  |   | INTERNAL<br>LOOPBACK<br>ENABLE | IRQ<br>ENABLE | LOOPBACK<br>RI INPUT | RTS | DTR |

| DEFAULT | 0 0 0    |  |   | 0                              | 0             | 0                    | 0   | 0   |

| BIT | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-5 | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4   | <ul> <li>Internal Loopback Enable. When this bit is set to logic 1, the UART enters diagnostic mode, as follows:</li> <li>(1) SOUT is forced to logic 1, and SIN is isolated from the communication link.</li> <li>(2) The modem output pins are set to their inactive state.</li> <li>(3) The modem input pins are isolated from the communication link and connect internally as DTR (bit 0 of HCR) →DSR#, RTS (bit 1 of HCR) →CTS#, Loopback RI input (bit 2 of HCR) → RI# and IRQ enable (bit 3 of HCR) →DCD#.</li> <li>Aside from the above connections, the UART operates normally. This method allows the CPU to test the UART in a convenient way.</li> </ul> |

| 3   | <b>IRQ Enable.</b> The UART interrupt output is enabled by setting this bit to logic 1. In diagnostic mode, this bit is internally connected to the modem control input DCD#.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2   | <b>Loopback RI Input.</b> This bit is only used in the diagnostic mode. In diagnostic mode, this bit is internally connected to the modem control input RI#.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1   | RTS (Request to Send). This bit controls the RTS# output. The value of this bit is inverted and output to RTS#.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0   | <b>DTR (Data Terminal Ready).</b> This bit controls the DTR# output. The value of this bit is inverted and output to DTR#.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

# 7.4 Handshake Status Register (HSR) (Read/Write)

This register reflects the current state of four input pins used with handshake peripherals such as modems and records changes on these pins.

| BIT     | 7   | 6  | 5   | 4   | 3    | 2    | 1    | 0    |

|---------|-----|----|-----|-----|------|------|------|------|

| NAME    | DCD | RI | DSR | стѕ | TDCD | FERI | TDSR | TCTS |

| DEFAULT | NA  | NA | NA  | NA  | NA   | NA   | NA   | NA   |

| BIT | DESCRIPTION                                                                                                                     |

|-----|---------------------------------------------------------------------------------------------------------------------------------|

| 7   | <b>DCD (Data Carrier Detect).</b> This bit is the inverse of the DCD# input and is equivalent to bit 3 of HCR in Loopback mode. |

| 6   | RI (Ring Indicator). This bit is the inverse of the RI# input and is equivalent to bit 2 of HCR in Loopback mode.               |

| 5   | <b>DSR (Data Set Ready).</b> This bit is the inverse of the DSR# input and is equivalent to bit 0 of HCR in Loopback mode.      |

| 4   | CTS (Clear to Send). This bit is the inverse of the CTS# input and is equivalent to bit 1 of HCR in Loopback mode.              |

| 3   | <b>TDCD (DCD# Toggling).</b> This bit indicates that the state of the DCD# pin has changed after HSR is read by the CPU.        |

| 2   | <b>FERI (RI Falling Edge).</b> This bit indicates that the RI# pin has changed from low to high after HSR is read by the CPU.   |

| 1   | <b>TDSR (DSR# Toggling).</b> This bit indicates that the state of the DSR# pin has changed after HSR is read by the CPU.        |

| 0   | TCTS (CTS# Toggling). This bit indicates that the state of the CTS# pin has changed after HSR is read by the CPU.               |

# 7.5 UART FIFO Control Register (UFR) (Write only)

This register is used to control the FIFO functions of the UART.

| BIT     | 7   | 6   | 5        | 4  | 3                     | 2                         | 1                         | 0              |

|---------|-----|-----|----------|----|-----------------------|---------------------------|---------------------------|----------------|

| NAME    | MSB | LSB | RESERVED |    | DMA<br>MODE<br>SELECT | TRANSMITTER<br>FIFO RESET | RECEIVER<br>FIFO<br>RESET | FIFO<br>ENABLE |

| DEFAULT | 0   | 0   | NA       | NA | 0                     | 0                         | 0                         | 0              |

| BIT | DESCRIPTION                                                                                                                                                                                            |                                                                                                                              |  |  |  |  |  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7   | MSB (RX Interrupt Active Level).                                                                                                                                                                       | These two bits are used to set the active level of the receiver FIFO interrupt. The active level is the number of bytes that |  |  |  |  |  |

| 6   | LSB (RX Interrupt Active Level).                                                                                                                                                                       | must be in the receiver FIFO to generate an interrupt.                                                                       |  |  |  |  |  |

| 5-4 | RESERVED.                                                                                                                                                                                              |                                                                                                                              |  |  |  |  |  |

| 3   | <b>DMS MODE SELECT.</b> When this bit is set to logic 1, DMA mode changes from mode 0 to mode 1 if UFR bit 0 = 1.                                                                                      |                                                                                                                              |  |  |  |  |  |

| 2   | <b>TRANSMITTER FIFO RESET.</b> Setting this bit from logic 0 to logic 1 resets the TX FIFO counter logic to its initial state, then needs set this bit from logic 1 to logic 0 to finish this "reset". |                                                                                                                              |  |  |  |  |  |

| 1   | <b>RECEIVER FIFO RESET.</b> Setting this bit from logic 0 to logic 1 resets the RX FIFO counter logic to its initial state, then needs set this bit from logic 1 to logic 0 to finish this "reset".    |                                                                                                                              |  |  |  |  |  |

| 0   | <b>FIFO ENABLE.</b> This bit enables 16550 (FI before other UFR bits are programmed.                                                                                                                   | FO) mode. This bit should be set to logic 1                                                                                  |  |  |  |  |  |

| UFR_  | UFR_  | RX FIFO INTERRUPT ACTIVE LEVEL (BYTES)  |                                         |                                         |                                         |  |  |  |

|-------|-------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|--|--|--|

| BIT 7 | BIT 6 | FIFO_LEVEL_<br>MODE<br>(CRF8_B7:6 = 00) | FIFO_LEVEL_<br>MODE<br>(CRF8_B7:6 = 01) | FIFO_LEVEL_<br>MODE<br>(CRF8_B7:6 = 10) | FIFO_LEVEL_<br>MODE<br>(CRF8_B7:6 = 11) |  |  |  |

| 0     | 0     | 01                                      | 16                                      | 80                                      | 112                                     |  |  |  |

| 0     | 1     | 04                                      | 32                                      | 88                                      | 116                                     |  |  |  |

| 1     | 0     | 08                                      | 48                                      | 96                                      | 120                                     |  |  |  |

| 1     | 1     | 14                                      | 64                                      | 104                                     | 124                                     |  |  |  |

# 7.6 Interrupt Status Register (ISR) (Read only)

This register reflects the UART interrupt status.

| BIT     | 7       | 6                  | 5 | 4                            | 3                            | 2                            | 1                            | 0 |

|---------|---------|--------------------|---|------------------------------|------------------------------|------------------------------|------------------------------|---|

| NAME    | FIFOS E | S ENABLED RESERVED |   | INTERRUPT<br>STATUS<br>BIT 2 | INTERRUPT<br>STATUS<br>BIT 1 | INTERRUPT<br>STATUS<br>BIT 0 | 0 IF<br>INTERRUPT<br>PENDING |   |

| DEFAULT | 0       | 0                  | 0 | 0                            | 0                            | 0                            | 0                            | 1 |

| BIT DESCRIPTION |

|-----------------|

|-----------------|

| 7-6 | FIFOS ENABLED. Set to logical 1 when UFR, bit 0 = 1.                                                                                                                             |                                                                                            |  |  |  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--|--|--|

| 5-4 | RESERVED.                                                                                                                                                                        |                                                                                            |  |  |  |

| 3   | INTERRUPT STATUS BIT 2. In 16450 mode, this bit is logical 0. In 16550 mode, bits 3 and 2 are set to logical 1 when a time-out interrupt is pending. Please see the table below. |                                                                                            |  |  |  |

| 2   | INTERRUPT STATUS BIT 1.                                                                                                                                                          | These two bits identify the priority level of the pending interrupt, as shown in the table |  |  |  |

| 1   | INTERRUPT STATUS BIT 0.                                                                                                                                                          |                                                                                            |  |  |  |

| 0   | <b>0 IF INTERRUPT PENDING.</b> This bit is logic 1 if there is no interrupt pending. If one of the interrupt sources has occurred, this bit is set to logical 0.                 |                                                                                            |  |  |  |

|          | IS       | R        |          | INTERRUPT SET AND FUNCTION |                        |                                                                                       |                                                          |  |  |

|----------|----------|----------|----------|----------------------------|------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------|--|--|

| Bit<br>3 | Bit<br>2 | Bit<br>1 | Bit<br>0 | Interrupt<br>priority      | Interrupt Type         | Interrupt Source                                                                      | Clear Interrupt                                          |  |  |

| 0        | 0        | 0        | 1        | -                          | -                      | No Interrupt pending                                                                  | -                                                        |  |  |

| 0        | 1        | 1        | 0        | First                      | UART Receive<br>Status | 1. OER = 1 2. PBER = 1<br>3. NSER = 1 4. SBD = 1                                      | Read USR                                                 |  |  |

| 0        | 1        | 0        | 0        | Second                     | RBR Data Ready         | RBR data ready     FIFO interrupt active level reached                                | Read RBR     Read RBR until FIFO data under active level |  |  |

| 1        | 1        | 0        | 0        | Second                     | FIFO Data Timeout      | Data present in RX FIFO for 4 characters period of time since last access of RX FIFO. | Read RBR                                                 |  |  |

| 0        | 0        | 1        | 0        | Third                      | TBR Empty              | TBR empty                                                                             | Write data into TBR     Read ISR (if priority is third)  |  |  |

| 0        | 0        | 0        | 0        | Fourth                     | Handshake status       | 1. TCTS = 1 2. TDSR = 1<br>3. FERI = 1 4. TDCD = 1                                    | Read HSR                                                 |  |  |

<sup>\*\*</sup> Bit 3 of ISR is enabled when bit 0 of UFR is logical 1.

# 7.7 Interrupt Control Register (ICR) (Read/Write)

This 8-bit register enables and disables the five types of controller interrupts separately. A selected interrupt can be enabled by setting the appropriate bit to logical 1. The interrupt system can be totally disabled by setting bits 0 through 3 to logical 0.

| BIT     | 7               | 6       | 5    | 4    | 3     | 2     | 1      | 0     |

|---------|-----------------|---------|------|------|-------|-------|--------|-------|

| NAME    | En_address_byte | RX_ctrl | RESE | RVED | EHSRI | EUSRI | ETBREI | ERDRI |

| DEFAULT | 0               | 0       | 0    | 0    | 0     | 0     | 0      | 0     |

| BIT | DESCRIPTION                                                                                                                                                                   |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | En_address_byte.  0: Tx block will send data byte. (If enable 9bit mode function CRF2 Bit0=1)  1: Tx block will send address byte. (If enable 9bit mode function CRF2 Bit0=1) |

| 6   | RX_ctrl.  0: Rx block could receive data byte. (If enable 9bit mode function CRF2 Bit0=1)  1: Rx block could receive address byte. (If enable 9bit mode function CRF2 Bit0=1) |

| 5-4 | RESERVED.                                                                                                                                                                     |

| BIT | DESCRIPTION                                                                                                                    |

|-----|--------------------------------------------------------------------------------------------------------------------------------|

| 3   | <b>EHSRI (Handshake Status Interrupt Enable).</b> Set this bit to logical 1 to enable the handshake status register interrupt. |

| 2   | <b>EUSRI (UART Receive Status Interrupt Enable).</b> Set this bit to logical 1 to enable the UART status register interrupt.   |

| 1   | <b>ETBREI (TBR Empty Interrupt Enable).</b> Set this bit to logical 1 to enable the TBR empty interrupt.                       |

| 0   | <b>ERDRI (RBR Data Ready Interrupt Enable).</b> Set this bit to logical 1 to enable the RBR data ready interrupt.              |

# 7.8 Programmable Baud Generator (BLL/BHL) (Read/Write)

Two 8-bit registers, BLL and BHL, compose a programmable baud generator that uses 24 MHz to generate a 1.8461 MHz frequency and divide it by a divisor from 1 to  $(2^{16} - 1)$ . The output frequency of the baud generator is the baud rate multiplied by 16, and this is the base frequency for the transmitter and receiver. The table below illustrates the use of the baud generator with a frequency of 1.8461 MHz. In high-speed UART mode (CRF0, bits 1 and 0), the programmable baud generator directly uses 24 MHz and the same divisor as the normal speed divisor. As a result, in high-speed mode, the data transmission rate can be as high as 1.5M bps.

|                           | BAUD RATE FROM DIFFERENT PRE-DIVIDER |                                                  |                  |  |  |

|---------------------------|--------------------------------------|--------------------------------------------------|------------------|--|--|

| Pre-Div: 13<br>1.8461M Hz | Pre-Div: 1.0<br>24M Hz               | Decimal divisor used<br>to generate 16X<br>clock | Error Percentage |  |  |

| 50                        | 650                                  | 2304                                             | **               |  |  |

| 75                        | 975                                  | 1536                                             | **               |  |  |

| 110                       | 1430                                 | 1047                                             | 0.18%            |  |  |

| 134.5                     | 1478.5                               | 857                                              | 0.099%           |  |  |

| 150                       | 1950                                 | 768                                              | **               |  |  |

| 300                       | 3900                                 | 384                                              | **               |  |  |

| 600                       | 7800                                 | 192                                              | **               |  |  |

| 1200                      | 15600                                | 96                                               | **               |  |  |

| 1800                      | 23400                                | 64                                               | **               |  |  |

| 2000                      | 26000                                | 58                                               | 0.53%            |  |  |

| 2400                      | 31200                                | 48                                               | **               |  |  |

| 3600                      | 46800                                | 32                                               | **               |  |  |

| 4800                      | 62400                                | 24                                               | **               |  |  |

| 7200                      | 93600                                | 16                                               | **               |  |  |

| 9600                      | 124800                               | 12                                               | **               |  |  |

| 19200                     | 249600                               | 6                                                | **               |  |  |

| 38400                     | 499200                               | 3                                                | **               |  |  |

| 57600                     | 748800                               | 2                                                | **               |  |  |

| 115200                    | 1497600                              | 1                                                | **               |  |  |

<sup>\*\*</sup> Unless specified, the error percentage for all of the baud rates is 0.16%.

Note: Pre-Divisor is determined by CRF0 of UART A.

# 7.9 User-defined Register (UDR) (Read/Write)

This is a temporary register that can be accessed and defined by the user.

### 7.10 Extendding FIFO

We support FIFO size extending to 128bytes for RX and TX block. (Enable bit: CRF8, Bit0)

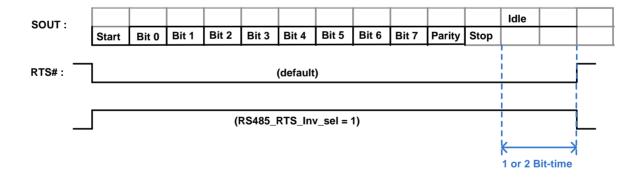

#### 7.11 UART RS485 Auto Flow Control